En este proyecto vamos a utilizar otra herramienta de Xilinx denominada “StateCAD”. Esta herramienta nos permite programar mediante un diagrama de estados, en este caso lo haremos de tipo Mealy.

El enunciado del proyecto es el siguiente:

Se desea proyectar el gobierno de un conmutador rotativo, que permite realizar un ciclo completo cuando el tambor haya efectuado una vuelta completa.

El disco solidario del tambor lleva un saliente para actuar sobre el contacto (a).

El pulsador (b) (botón de impulsos) da comienzo al ciclo.

1) Estado inicial (reposo) a=1, b=0, M=0.

2) (b) es accionado y después desaccionado rápidamente (impulso) -> M=1.

3) Cuando el disco ha dado una vuelta, (a) es accionado por el saliente y el disco se para.

Analizando el enunciado hacemos una tabla con los estados estables para guiarnos a la hora de realizar el diagrama de flujo en el entorno "StateCAD".

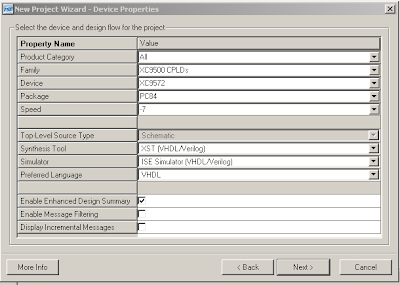

Comenzamos, como en los ejercicios anteriores, abriendo Xilinx y creando un nuevo proyecto “File/ New Project” y lo damos el nombre de “mealy_2011” .

La configuración del CPLD como en los anteriores.

Una vez tengamos creado el nuevo proyecto, damos clic derecho sobre él y seleccionamos “New Source”.

Creamos un “State Diagram” con el nombre “rota”.

Damos a “Next” y finalmente el solo nos abrirá el entorno StateCAD.

Una vez dentro, vamos a “Options / Variable” y creamos las variables poniendo el tipo de pin que son.

Configuramos “A” y “B” como entradas , declaramos también el reloj “CLK” y los estados ”StateX”.

Por ejemplo “M” es una salida con registro porque la máquina es síncrona, es decir, la salida no hace caso a la entrada hasta que no la llega un ciclo de reloj.

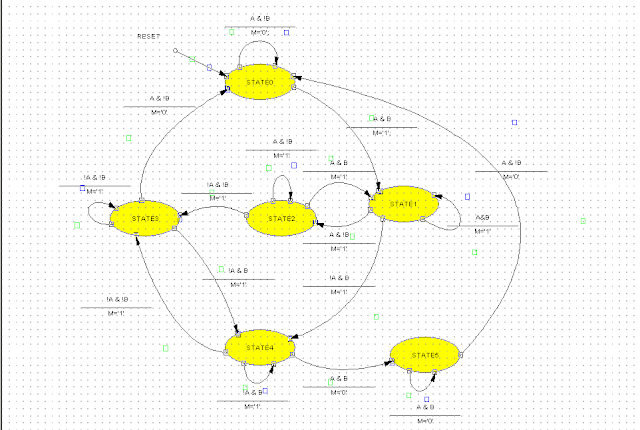

A continuación colocamos los estados con la herramienta “Add State”.

Ahora seleccionamos la herramienta “Add Transition” y vamos estableciendo las uniones necesarias. Para realizar líneas curvas podemos hacer una recta y después curvarla seleccionándola manualmente o bien hacer clic izquierdo en diferentes puntos antes de unir la línea con su destino.

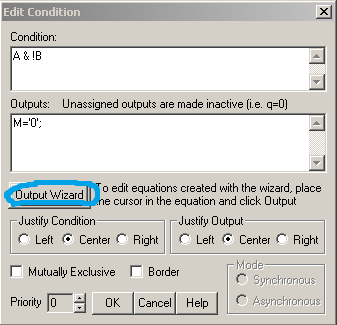

Para establecer la condición de la unión que hemos creado, damos doble clic sobre la flecha y se nos abrirá una ventana donde introduciremos el estado de las entradas y de la salida.

La salida podemos configurarla desde “Output Wizard”, pero en este ejercicio lo vamos a poner directamente con el nombre de la variable de la salida igualada a su valor, 0 o 1 , entre comillas simples y finalizado por punto y coma “M=’0’; “.

La condición que han de cumplir las entradas es que “A” esté en 1 y “B” esté en 0, para ello ponemos las dos variables separadas con un ampersan que establece la operación lógica AND y una exclamación final “ ! “ delante de la variable “B” para negarla.

Vamos poniendo las condiciones en cada una de las uniones .

Ahora vamos a poner el “Reset” en el “STATE0” para controlar en qué estado comienza al encender.

Para ello utilizamos la herramienta “Add Reset”.

Nuestro “reset” va a ser asíncrono y va a funcionar en alto activo (por defecto trabaja en alto activo).

Todo esto trabaja por debajo con código VHDL, Abel ó Verilog.

En la parte superior de la página veremos una pestaña donde podemos elegir el código, en nuestro caso vamos a seleccionar “VHDL”.

Existen también plantillas de máquinas de estado que nos pueden facilitar trabajo en ciertas ocasiones.

Para ello clicamos en “Draw State Machines”.

Tras realizar todas las conexiones necesarias nos queda algo así.

Lo siguiente va a ser simular el funcionamiento del diagrama de estados antes de irnos a “ISE”.

Para ello vamos a “State Bench”.

Nos aparecerá otra ventana donde se irá mostrando en una gráfica como va reaccionando el diagrama de estados.

Al hacer clic sobre una transición del diagrama esta se pondrá verde, eso significa que estamos fijando como cumplida su condición. La zona que vemos amarilla, es decir, el “State1” y la condición “ A&B M=’1’ ” significa que se encuentra en espera en ese estado.

Tenemos que ir dando los pulsos de reloj manualmente en “Cycle”.

También podemos resetear en “Reset”.

Una vez hemos comprobado que todo funciona como queremos generamos el VHDL para llevarlo al esquemático de Xilinx.

Para ello clicamos en “Generate HDL” y nos mostrará el programa en formato “VHDL”.

Volvemos al “ISE” y en nuestro proyecto damos clic derecho, “Add Source” y seleccionamos el archivo “.VHD” que acabamos de crear.

Veremos que se ha añadido a nuestro proyecto.

A partir de ese archivo vamos a crear un nuevo símbolo.

También tenemos que crear un esquemático dentro de nuestro proyecto. Para ello damos clic derecho sobre el proyecto, seleccionamos “New Source” y creamos un esquemático con el nombre de ” rotaESQUEM”.

Seleccionamos el archivo “ROTA.vhd” y damos a “Create Schematic Symbol” en “Design Utilities”. Una vez hecho esto ya tendremos el símbolo “ROTA”.

Ahora ya solo queda introducir el símbolo “ROTA” en nuestro esquemático y ponerle los buffer, nombres y etiquetas I/O tal y como hemos hecho en ejercicios anteriores.

El esquema quedará así.

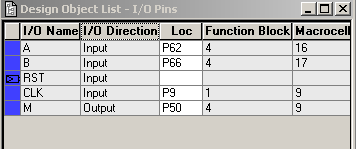

Para asignar los pines creamos el “.ucf”, damos clic derecho en el proyecto, seleccionamos “New Source”, “ Implementation Constraints File” y le damos el nombre de “ROTATIVA”.

Abrimos el “.ucf” creado y nos meterá en el “PACE” donde asignaremos los pines correspondientes.

Hacemos la simulación en tiempo real en “Post-Fit Simulation” y seleccionando “Simulate Post-Fit Mode” como ya se ha visto en proyectos anteriores.

Como podemos ver en la simulación el funcionamiento parece correcto dado que al pulsar “B” y estando en “A” no se para “M” hasta el siguiente flanco de subida de “A”.

Ya solo queda seguir el árbol de implementación hasta llegar al “Fit” y finalmente al “.JED”.