En este ejercicio vamos a utilizar una máquina de estados de tipo Moore.

Haremos el diagrama de flujo con sus estados estables e inestables mediante la herramienta StateCAD de Xilinx.

El ejercicio consiste en detectar una secuencia “1,0,1,1”, estará compuesto de una entrada “a” y una salida “S”.

Los pulsos de reloj los introduciremos de forma manual mediante un interruptor.

Abrimos Xilinx y damos a “File / New Project”, ponemos el nombre de nuestro proyecto, en este caso “DETECTOR_MOORE” y configuramos las especificaciones de nuestro dispositivo.

También seleccionamos el tipo de lenguaje que vamos a utilizar, en este caso “HDL”.

En la siguiente ventana seleccionaremos “New Source” y añadiremos una nueva fuente que será el diagrama de estados.

Ponemos un nombre a la nueva fuente, en este caso “Detector_Moore” y seleccionamos “State Diagram”.

Una vez creado pasaremos al entorno “StateCAD”, cuando estemos dentro seleccionamos “Options/ Variable” y declararemos las variables que vamos a utilizar.

Pondremos “a “ como entrada por donde introduciremos la secuencia, “CLK “ el reloj que en este ejercicio será manual y “S “ que será la salida por donde nos saque un 1 al completarse la secuencia.

La salida la hemos puesto con registro para que se mantenga encendida hasta dar el siguiente pulso de reloj.

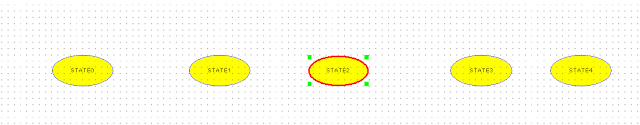

Una vez hemos declarado ya las variables vamos a la herramienta “Add State” y colocamos los 5 estados que necesitamos .

Cuando estén colocados los estados vamos a la herramienta “Add Transition” y establecemos las transiciones necesarias entre estados.

Los cuadrados pequeños que se ven al lado de las transiciones son puntos que podemos establecer para que la línea se incline hacia ellos y quede curvada, Se hacen con solo hacer clic con el ratón en la posición que queramos antes de llevar la transición su destino.

Una vez hecho esto vamos a la herramienta “Add Reset” y establecemos el lugar de reseteo para controlar el estado de inicio del programa.

Configuramos el reset como asíncrono y de alto activo, para lo cual lo igualamos a 1 con comillas simples “ RESET=’1’ “.

Quedaría así.

Ahora configuramos los estados estables e inestables dando doble clic sobre los globos o las transiciones. En las transiciones pondremos el estado de a, “ a=’0’ ” o bien “a=’1’ ”, en los globos pondremos el estado de la salida S, “ S =’0’ “ ó “ S=’1’ “.

Nos quedará así.

Ahora vamos a hacer la simulación clicando sobre “ State Bench”.

Vamos seleccionando la transición que queremos que se cumpla y damos a “Cycle”, una vez el simulador ha pasado por ahí nos aparecerá en verde, las zonas por las que aún no hemos pasado aparecerán en rojo.

Podemos seleccionar también “Reset” para utilizar el reseteo de nuestro diagrama o “ Restart” para reiniciar la simulación.

Se ve en la gráfica como la salida “S” se activa cuando se completa la secuencia.

Una vez ya hemos comprobado que funciona como queremos seleccionamos “ Generate HDL” para compilar el archivo “VHDL” que pasaremos a Xilinx ISE.

Nos lo muestra.

Ahora volvemos al proyecto que habíamos creado en ISE y damos clic derecho sobre él y “ Add Source”.

Seleccionamos el documento en extensión “ .VHD” que nos acaba de compilar StateCAD.

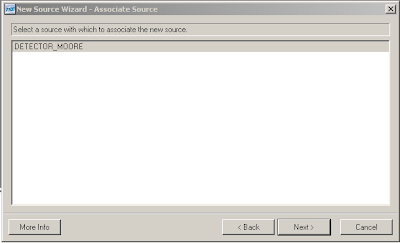

Seguidamente volvemos a dar clic derecho sobre el proyecto y seleccionamos “New Source”, creamos el “ Test Bench Waveform” para la simulación en ISE.

En la siguiente ventana seleccionamos nuestro proyecto.

Configuramos el estado de las entradas para ver el funcionamiento con respeto a ellas, yo he puesto un ciclo completo con el reset a 1 y otro ciclo completo con el reset a 0, de esta forma puedo ver si mi reset está bien configurado en alto activo como yo quiero.

Con el modo implementación seleccionado podemos ver el símbolo de nuestro programa en el apartado de “Process “ “Synthesize – XST”

Creamos ahora el “.UCF” para establecer cuáles serán los pines reales que vamos a utilizar en el CPLD.

Para ello volvemos a seleccionar “New Source” en nuestro proyecto y esta vez creamos un “ Implementation Constraints File”.

Se abre el entorno PACE y ahí colocamos los pines asociados a cada variable.

Una vez ya hemos colocado los pines vamos a la simulación con retardos reales.

Seleccionado el modo “Post Fit-Simulation”, en la parte superior del proyecto, seleccionamos “Simulate Post-Fit Mode”.

Nos crea automáticamente el Fit antes de pasar a la simulación , el cual es un documento en el que aparece toda la información sobre nuestro proyecto,

Finalmente nos muestra la simulación con retardos reales.

Podemos comprobar que el reset realiza la función como queríamos, así luego no nos llevamos sorpresas una vez programado, y la salida se pone en 1 cuando se completa la secuencia.

Por último seleccionamos “Generate Programing File” y generamos el “.JED” para programar con el Impact.