Vamos a diseñar un contador decodificado para un display 7 segmentos.

Como hemos hecho anteriormente, desde Xilinx ISE vamos a “File/New Project”, lo llamaremos “contadorBCD” y seleccionaremos modo esquemático.

Daremos a siguiente y seleccionaremos ” New Source”, nos aparecerá otra ventana donde seleccionaremos el modo esquemático y lo pondremos el mismo nombre que antes.

Una vez abierto el esquemático insertaremos un “CD4CE”, con un “BUFG” para el reloj y un “BUFGSR” para el clear.

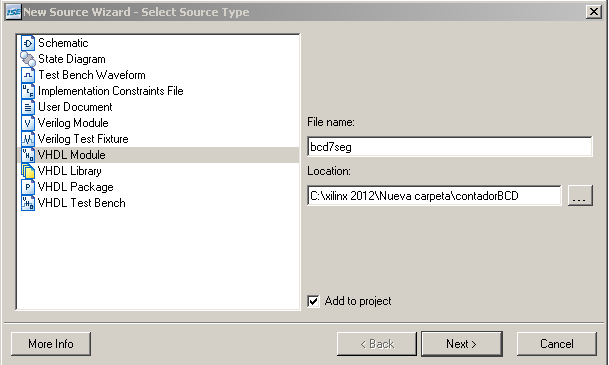

Ahora vamos a crear un nuevo símbolo en VHDL, este va a ser el decodificador 7 segmentos. Para ello desde el proyecto damos click derecho y “New Source”, elegimos ” VHDL Module” y ponemos el nombre de “bcd7seg”.

Seleccionamos las entradas, que son 4( de 0 a 3) y las salidas que son 7(de 0 a 6).

Nos aparecerá una nueva fuente con un código VHDL, en el cual tendremos que introducir el código para que realice la función deseada, en este caso decodificador BCD 7 segmentos.

El propio Xilinx nos ofrece plantillas para utilizar en VHDL, para

ello vamos a “Edit/Language Templates”.

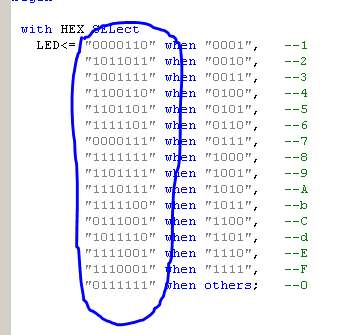

Dentro del apartado “VHDL/ Synthesis Constructs/ Coding Examples/ Misc” encontramos la plantilla “7-Segment Display Hex Convers” y copiamos su código.

Vamos a la nueva fuente que habíamos creado anteriormente y copiamos el código de la plantilla entre “begin” y “end Behavioral;”

El código que hemos cogido está creado para Display de ánodo común y el nuestro es de cátodo común, consecuentemente vamos a tener que cambiar los “1” por “0” y viceversa a la salida.

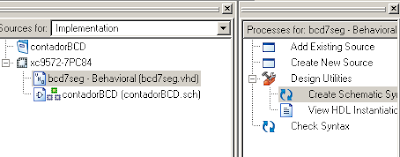

Una vez hecho esto vamos a añadir nuestro código VHDL a los símbolos para poderlo utilizar en nuestro esquemático, para ello seleccionamos nuestra fuente VHDL “bcd7seg” y en “Design Utilities” damos a “Create Schematic Symbol”.

Ahora nos aparecerá el componente “bcd7seg” dentro de los símbolos.

Añadiremos el símbolo a nuestro esquemático y pondremos las conexiones, los nombres y las etiquetas necesarias.

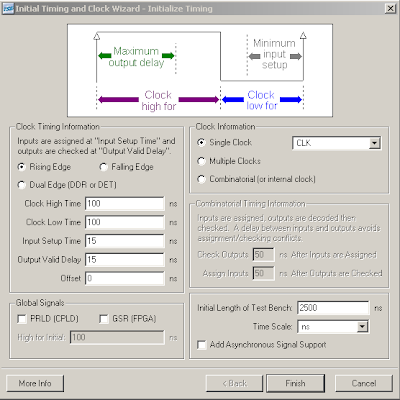

A continuación crearemos el fichero “Test Bench Waveform” para la simulación. Para ello damos click derecho sobre el proyecto, seleccionamos “New Source” y creamos el “Test Bench Waveform” con el nombre “tb_contadorBCD”.

Ponemos 2500 ns para poder ver el ciclo completo.

Configuramos la posición de las entradas para la simulación.

Vamos a realizar la simulación con retrasos reales de tiempo, para ello vamos a “Xilix ISE Simulator” y damos doble click en ” Simulate Post-Fit Model”.

En el apartado” Synthetize-XST” nos aparece un aviso, para ver a que se debe vamos a “View Synthesis Report”.

Nos aparecerá un aviso pero nos damos cuenta de que nos avisa de circunstancias que ya habíamos tenido en cuenta en el diseño, como que el pin “CEO” no tiene ninguna conexión o que se ha añadido un “OBUF” al pin “TC”.

A continuación crearemos el “.ucf ” desde el cual asignaremos la posición real de las entradas y salidas en los pines del CPLD. Para ello damos click derecho sobre el proyecto y seleccionamos “New Source” , “Implementation Constraints File” y lo ponemos el nombre de “contabcdufc”.

Una vez creado damos doble click sobre él y se nos abrirá el entorno “PACE” desde el cual colocaremos las entradas y salidas en sus pines correspondientes, el “CLR” lo dejamos libre ya que es asignado internamente al pin nº74.

Finalmente damos a “Translate” y seguidamente a “FIT” y nos aparecerá el documento con todos los datos de nuestro diseño.

Tambien podemos ver el símbolo final de nuestro diseño desde “View Technology Schematic” en “Synthetize- XST”.