Lo primero que haremos será descargar la versión 10.1 SP3 y la 13.2 de Xilinx, para lo cual iremos a la página www.xilinx.com, descargaremos el software y nos registraremos para que nos envíen las licencias.

El primer proyecto va a ser un sumador binario de 1bit empleando una herramienta de esquemáticos integrada en “ISE” llamada “ECS”.

Ahora vamos a crear un nuevo proyecto y configurarlo. Para ello iremos a “File\New Project”.

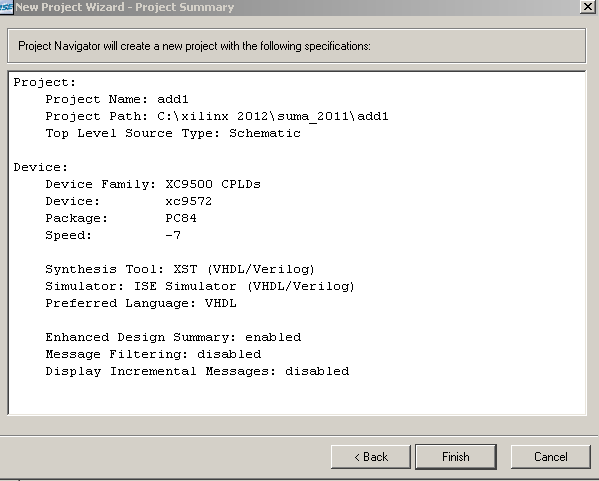

Seleccionamos el nombre del proyecto, el directorio y el tipo, que en este caso será gráfico y damos a “Next”.

Ahora nos aparecerá la siguiente ventana.

Aquí seleccionaremos nuestro CPLD.

-FAMILY: La familia a la que pertenece nuestro CPLD, en este caso “XC9500 CPLD´s”.

-DEVICE: Modelo del CPLD, seleccionamos el “XC9572”.

-PACKAGE: El tipo de encapsulado, en este caso “PC 84”.

-SPEED: Seleccionamos el retardo pin a pin en nanosegundos, será -7.

SYNTHESIS TOOL: Sintetizador “XST (VHDL/Verilog) ”.

SIMULATOR: En este caso usaremos el simulador de Xilinx, el ISE “Simulator (VHDL/Verilog)”.

PREFERRED LANGUAGE: seleccionamos “VHDL”.

Damos a “Next” hasta que finalmente aparezca una ventana con las especificaciones de nuestro proyecto.

Ahora añadiremos una nueva fuente de esta manera:

Y en la siguiente ventana pondremos un nombre y seleccionaremos esquemático.

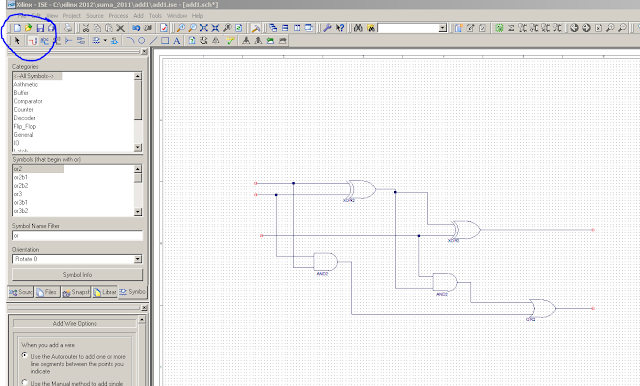

Seguidamente comenzaremos ya a hacer nuestro esquemático, seleccionamos la pestaña “Symbol” y en “Categories” encontraremos los tipos de componentes que podemos utilizar.

Donde aparece la “X” azul iremos haciendo nuestro circuito.

Introducimos los componentes necesarios, en este caso dos puertas “XOR2”, una “OR2” y dos “AND2” y lo conexionamos todo con la herramienta “Add Wire”.

Ahora vamos a poner nombres a las líneas de entrada y de

salida, para ello seleccionamos “Add Net Name”, escribimos un nombre y lo colocamos en la que queramos.

Seleccionamos arriba la herramienta, en “Name” ponemos el nombre que vamos a poner y el cursor del ratón tomará ese nombre y lo colocaremos donde queramos (en la captura no aparece el ratón, pero está en la misma posición que “Cout”).

Vamos a marcar las entradas y salidas del CPLD, estas pueden ser de tipo entrada, salida o bidireccional. Para ello seleccionamos “Add I/O Marker”.

Las colocamos en modo automático y finalmente comprobamos si hay errores.

Si todo es correcto nos aparecerá el mensaje “No error or warning is detected”.

Lo siguiente que haremos será realizar una simulación funcional del circuito que hemos diseñado, para ello usaremos el propio simulador de Xilinx “ ISE Simulator (VHDL/Verilog)”. Para simular, nuestro esquemático será traducido a Lenguaje Descriptivo Hardware (HDL), en concreto a VHDL. Para esto hacemos como antes, clicamos botón derecho del raton sobre nuestro proyecto y seleccionamos “New Source”, pero esta vez seleccionamos “Test Bench Waveform”.

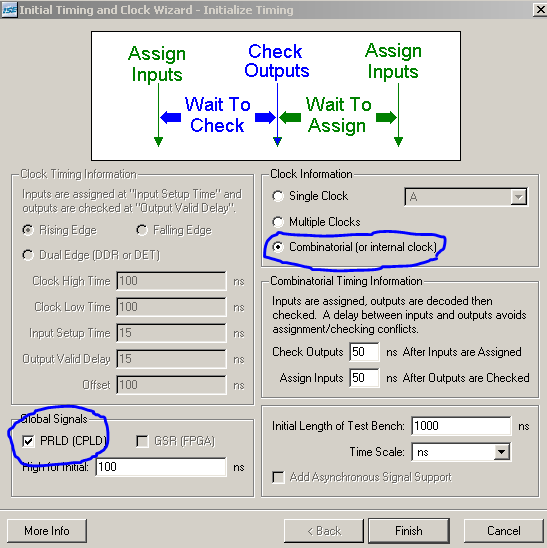

Damos a “Next” y a “Finish” y nos aparecerá una ventana que configuraremos de la siguiente manera.

Seguidamente seleccionamos los estados de las entradas y lo guardamos.

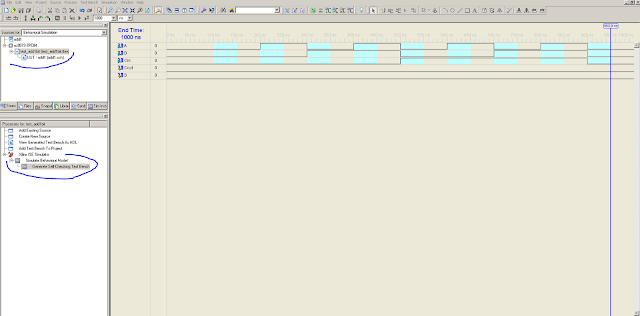

Ahora vamos a ” Xilinx ISE Simulator”, abrimos la pestaña y seleccionamos “Generate Self-Cheking Test Bench”.

Nos aparecerá la simulación .

También podemos ver el VHDL de nuestro esquema, para ello selecionaremos “View HDL Funcional Mode”.

Lo siguiente va a ser colocar las entradas y salidas en los pines que nos convengan, para ello vamos a “Floorplan IO-Pre-Syntesis”.

Se abrirá el entorno “Xilins PLACE” e iremos arrastrando las

entradas y salidas donde queramos.

Guardamos los cambios y cuando nos salga la siguiente ventana damos a OK.

Vamos siguiendo el esquema y nos creara un archivo con los datos de nuestro programa con la función “Fit”. En este informe podemos encontrar el sumario, errores o avisos, lógica, lista de pines… etc.

Finalmente crearemos el archivo en extensión .JED seleccionando “Generate Programming File”.